# TOSHIBA MOS MEMORY PRODUCTS

16384 WORD x 1 BIT DYNAMIC RAM

N CHANNEL SILICON GATE MOS

## TMM416P/D-2, TMM416P/D-3, TMM416P/D-4

#### DESCRIPTION

The TMM416P/D is a 16,384 words by 1 bit MOS random access memory circuit fabricated with TOSHIBA's double poly N-channel silicon gate process for high performance and high functional density

The TMM416P/D uses a single transistor dynamic storage cell and dynamic control circuitry to achieve high speed and low power dissipation. Multiplexed address inputs permit the TMM416P/D to be packaged in a standard 16 pin plastic and cerdip DIP. This package size provides high system bit densities and is compatible with widely available automatic testing and insertion equipment

#### **FEATURES**

- 16,384 words by 1 bit organization

- Fast access time and cycle time

| DEVICE      | trac   | tRC    |

|-------------|--------|--------|

| TMM416P/D-2 | 150 ns | 320 ns |

| TMM416P/D-3 | 200 ns | 375 ns |

| TMM416P/D-4 | 250 ns | 410 ns |

- Industry standard 16 pin DIP

- Standard ± 10% power supply (+12V, ± 5V)

- Lower power 462mW operating (max ) 20mW standby (max)

- · Output unlatched at cycle end allows two-dimensional chip select

- Common I/O capability using "Early Write" opera-

- Read-Modify-Write, RAS-only refresh, and Page-Mode capability

- All inputs and output TTL compatible

- 128 refresh cycles / 2 msec

- Compatible with MK4116

- Package

Plastic DIP TMM416P Cerdip DIP TMM416D

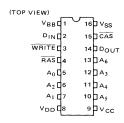

#### PIN CONNECTIONS

#### **PIN NAMES**

| A <sub>0</sub> .A <sub>6</sub> | Address Inputs        |

|--------------------------------|-----------------------|

| CAS                            | Column Address Strobe |

| DIN                            | Data In               |

| POUT                           | Data Out              |

| RAS                            | Row Address Strobe    |

| WRITE                          | Read/Write Input      |

| VBB                            | Power (-5V)           |

| vcc                            | Power (+5V)           |

| V <sub>DD</sub>                | Power (+12V)          |

| VSS                            | Ground                |

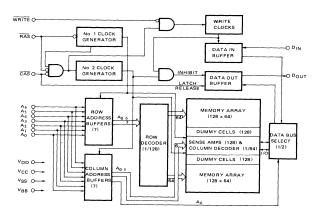

#### **BLOCK DIAGRAM**

#### **ABSOLUTE MAXIMUM RATINGS**

| RATING                                               |                                | VALUE      | UNITS  | NOTES |  |

|------------------------------------------------------|--------------------------------|------------|--------|-------|--|

| Voltage on any pin relative to V <sub>BB</sub>       |                                | -0 5 ~ +20 | V      | 1     |  |

| Voltage on V <sub>DD</sub> , V <sub>CC</sub> supplie | es relative to V <sub>SS</sub> | −1 0 ~ +15 | V      | 1     |  |

| $V_{BB}-V_{SS}$ $(V_{DD}-V_{SS}>0V)$                 |                                | 0          | V      | 1     |  |

| Operating temperature Storage temperature            |                                | 0~70       | °C     | 1     |  |

|                                                      |                                | -55 ~ 150  | °C     | 1     |  |

| Soldering temperature Time                           |                                | 260 10     | °C sec | 1     |  |

| Power dissipation                                    | TMM416P                        | 600        | mW     | T .   |  |

| rower dissipation                                    | TMM416D                        | 1000       | TIIVV  | 1 '   |  |

| Short circuit output current                         |                                | 50         | mA     | 1     |  |

### **RECOMMENDED DC OPERATING CONDITIONS** (Ta = $0 \sim 70^{\circ}$ C) (Note 2)

| SYMBOL           | PARAMETER                                  | MIN  | TYP  | MAX  | UNITS | NOTES |

|------------------|--------------------------------------------|------|------|------|-------|-------|

| V <sub>DD</sub>  |                                            | 108  | 12 0 | 13 2 | V     | 3     |

| Vcc              | Supply Voltage                             | 4 5  | 50   | 5 5  | V     | 3,4   |

| V <sub>SS</sub>  |                                            | 0    | 0    | 0    | V     | 3     |

| V <sub>BB</sub>  |                                            | -4 5 | -50  | -55  | V     | 3     |

| V <sub>IHC</sub> | Input High Voltage, RAS, CAS, WRITE        | 2 7  |      | 7 0  | V     | 3     |

| V <sub>IH</sub>  | Input High Voltage, except RAS, CAS, WRITE | 2 4  |      | 7 0  | V     | 3     |

| VIL              | Input Low Voltage, all inputs              | -10  |      | 0.8  | V     | 3     |

#### DC ELECTRICAL CHARACTERISTICS

$(V_{DD} = 12~0V \pm ~10\%, V_{CC} = 5.0V \pm 10\%, V_{SS} = 0V, V_{BB} = -5.0V \pm 10\%, Ta = 0^{\circ}C \sim 70^{\circ}C)~(Note~2)$

| SYMBOL             | PARAMETER                                                                                                                               | MIN. | MAX. | UNITS | NOTES |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|-------|

| DD1                | OPERATING CURRENT                                                                                                                       |      | 35   | mA    | 5     |

| lcc1               | Average power supply operating current                                                                                                  |      |      |       | 6     |

| I <sub>BB1</sub>   | (RAS, CAS cycling t <sub>RC</sub> = mınımum value)                                                                                      |      | 200  | μΑ    |       |

| I <sub>DD2</sub>   | STANDBY CURRENT                                                                                                                         |      | 15   | mA    |       |

| lcc2               | Power supply standby current                                                                                                            | -10  | 10   | μΑ    |       |

| I <sub>BB2</sub>   | (RAS = V <sub>IHC</sub> , D <sub>OUT</sub> = High Impedance)                                                                            |      | 100  | μΑ    |       |

| I <sub>DD3</sub>   | REFRESH CURRENT                                                                                                                         |      | 27   | mA    | 5     |

| 1ссз               | Average power supply current, refresh mode                                                                                              | -10  | 10   | μΑ    |       |

| I <sub>BB3</sub>   | (RAS cycling, CAS = V <sub>IHC</sub> t <sub>RC</sub> = mınımum value)                                                                   |      | 200  | μΑ    |       |

| I <sub>DD4</sub>   | PAGE MODE CURRENT                                                                                                                       |      | 27   | mA    | 5     |

| I <sub>CC4</sub>   | Average power supply current, page mode operation                                                                                       |      |      |       | 6     |

| I <sub>BB4</sub>   | (RAS = V <sub>IL</sub> , CAS cycling t <sub>PC</sub> = minimum value)                                                                   |      | 200  | μΑ    |       |

| I <sub>I (L)</sub> | INPUT LEAKAGE CURRENT Input leakage current, any input $(V_{BB} = -5V)$ $OV \le V_{IN} \le +7 OV$ , all other pins not under test = OV) | -10  | 10   | μΑ    |       |

| l <sub>0</sub> (L) | OUTPUT LEAKAGE CURRENT ( $D_{OUT}$ is disabled, $OV \le V_{OUT} \le +5 5V$ )                                                            | -10  | 10   | μΑ    |       |

| Voн                | OUTPUT LEVELS Output "H" level voltage (IOUT = -5mA)                                                                                    | 2 4  |      | V     | 4     |

| Vol                | OUTPUT LEVELS Output "L" level voltage (IOUT = 4 2mA)                                                                                   |      | 0.4  | V     | 4     |

## **ELECTRICAL CHARACTERISTICS AND RECOMMENDED AC OPERATING CONDITIONS**

$(V_{DD} = 12.0V \pm 10\%, \ V_{CC} = 5.0V \pm 10\%, \ V_{SS} = OV, \ V_{BB} = -5.0V \pm 10\%, \ T_{a} = 0^{\circ}C \sim 70^{\circ}C)$

(NOTES 2, 7, 8, 10)

| SYMBOL           | PARAMETER                           | TMM | 416P/D-2 | TMM416P/D-3 |        | TMM416P/D-4 |        | LINUTC | NOTES  |

|------------------|-------------------------------------|-----|----------|-------------|--------|-------------|--------|--------|--------|

| STIVIBUL         | TAHAWETEH                           | MIN | MAX      | MIN         | MAX.   | MIN         | MAX    | UNITS  | NOTES  |

| tRC              | Random read or write cycle time     | 320 |          | 375         |        | 410         |        | ns     | 9      |

| tRWC             | Read-write cycle time               | 320 |          | 375         |        | 425         |        | ns     | 9      |

| t <sub>RMW</sub> | Read-modify-write cycle time        | 320 |          | 405         |        | 500         |        | ns     | 9      |

| tPC              | Page mode cycle time                | 170 |          | 225         |        | 275         |        | ns     |        |

| tRAC             | Access time from RAS                |     | 150      |             | 200    |             | 250    | ns     | 11, 13 |

| tcac             | Access time from CAS                | 1   | 100      |             | 135    |             | 165    | ns     | 12, 13 |

| toff             | Output buffer turn-off delay        | 0   | 40       | 0           | 50     | 0           | 60     | ns     | 14     |

| tΤ               | Transition time (rise and fall)     | 3   | 35       | 3           | 50     | 3           | 50     | ns     | 10     |

| t <sub>RP</sub>  | RAS precharge time                  | 100 |          | 120         |        | 150         |        | ns     |        |

| tras             | RAS pulse width                     | 150 | 32,000   | 200         | 32,000 | 250         | 32,000 | ns     |        |

| tRSH             | RAS hold time                       | 100 |          | 135         |        | 165         |        | ns     |        |

| tcsн             | CAS hold time                       | 150 |          | 200         |        | 250         |        | ns     |        |

| tcas             | CAS pulse width                     | 100 | 10,000   | 135         | 10,000 | 165         | 10,000 | ns     |        |

| tRCD             | RAS to CAS delay time               | 20  | 50       | 25          | 65     | 35          | 85     | ns     | 15     |

| tCRP             | CAS to RAS precharge time           | -20 |          | -20         |        | -20         | ,      | ns     |        |

| tasr             | Row Address set-up time             | 0   |          | 0           |        | 0           |        | ns     |        |

| trah             | Row Address hold time               | 20  |          | 25          |        | 35          |        | ns     |        |

| tASC             | Column Address set-up time          | -10 |          | -10         |        | -10         |        | ns     |        |

| tcah             | Column Address hold time            | 45  |          | 55          |        | 75          |        | ns     |        |

|                  | Column Address hold time            | 95  |          | 120         |        | 160         |        |        |        |

| tAR              | referenced to RAS                   | 95  |          | 120         |        | 160         |        | ns     |        |

| tRCS             | Read command set-up time            | 0   |          | 0           |        | 0           |        | ns     |        |

| <sup>t</sup> RCH | Read command hold time              | 0   |          | 0           |        | 0           |        | ns     |        |

| twcH             | Write command hold time             | 45  |          | 55          |        | 75          |        | ns     |        |

|                  | Write command hold time             | 95  |          | 120         |        | 160         |        |        |        |

| twcr             | referenced to RAS                   | 95  |          | 120         |        | 160         |        | ns     |        |

| twp              | Write command pulse width           | 45  |          | 55          |        | 75          |        | ns     |        |

| tRWL             | Write command to RAS lead time      | 50  |          | 70          |        | 85          |        | ns     |        |

| tcwL             | Write command to CAS lead time      | 50  |          | 70          |        | 85          |        | ns     |        |

| t <sub>DS</sub>  | Data-ın set-up time                 | 0   |          | 0           |        | 0           |        | ns     | 16     |

| tрн              | Data-ın hold time                   | 45  |          | 55          |        | 75          |        | ns     | 16     |

| <sup>t</sup> DHR | Data-in hold time referenced to RAS | 95  |          | 120         |        | 160         |        | ns     |        |

|                  | CAS precharge time (for page-       | 60  |          | 00          |        | 100         |        |        |        |

| tCP              | mode cycle only)                    | 60  |          | 80          |        | 100         |        | ns     |        |

| t <sub>REF</sub> | Refresh period                      |     | 2        |             | 2      |             | 2      | ms     |        |

| twcs             | Write command set-up time           | -20 |          | -20         |        | -20         |        | ns     | 17     |

| tcwD             | CAS to WRITE delay                  | 60  |          | 80          |        | 90          |        | ns     | 17     |

| t <sub>RWD</sub> | RAS to WRITE delay                  | 110 |          | 145         |        | 175         |        | ns     | 17     |

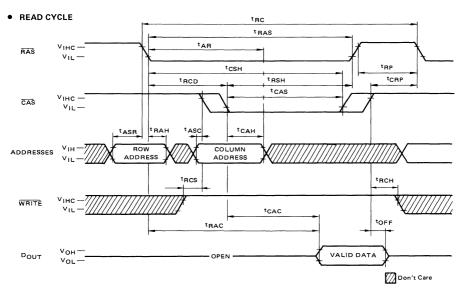

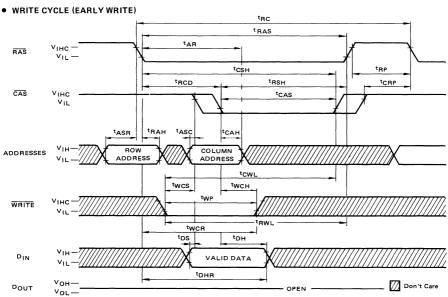

#### **TIMING WAVEFORMS**

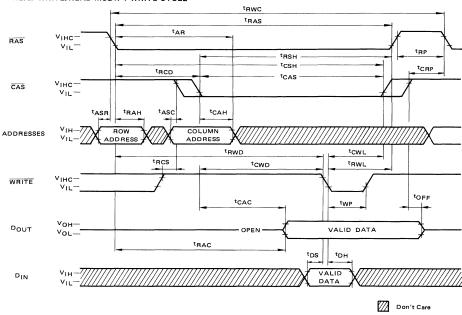

#### • READ-WRITE/READ-MODIFY-WRITE CYCLE

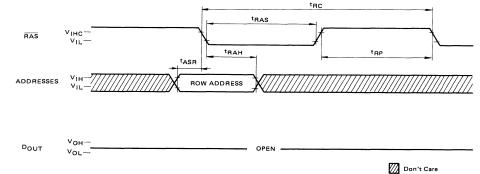

#### • "RAS-ONLY" REFRESH CYCLE

## Toshiba

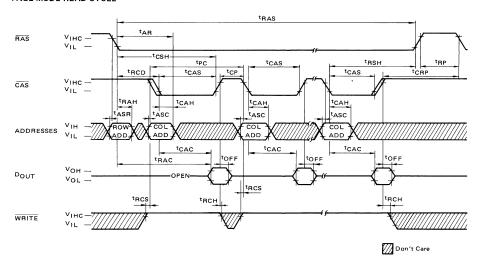

#### PAGE MODE READ CYCLE

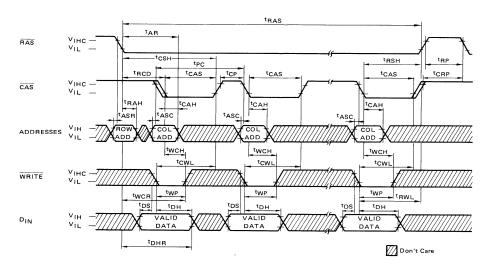

#### • PAGE MODE WRITE CYCLE

#### CAPACITANCE

$(V_{DD} = 12.0V \pm 10\%, V_{CC} = 5.0V \pm 10\%, V_{SS} = 0V, V_{BB} = -5.0V \pm 10\%, f = 1MHz, Ta = 0^{\circ}C \sim 70^{\circ}C)$

|   | SYMBOL          | PARAMETER                                                            | TYP | MAX | UNIT |

|---|-----------------|----------------------------------------------------------------------|-----|-----|------|

|   | C <sub>1</sub>  | Input Capacitance (A <sub>0</sub> -A <sub>6</sub> ), D <sub>IN</sub> | 4   | 5   | pΕ   |

| Ī | Cı <sub>2</sub> | Input Capacitance RAS, CAS, WRITE                                    | 8   | 10  | pF   |

|   | Co              | Output Capacitance (D <sub>OUT</sub> )                               | 5   | 7   | рF   |

#### POWER DERATING CHARACTERISTICS

#### NOTES

- 1 Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device

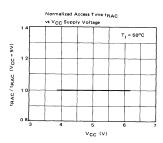

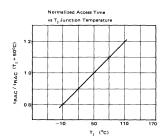

- 2 T $_a$  is specified here for operation at frequencies to  $t_{RC} \geqslant t_{RC}$  (min.) Operation at higher cycle rates with reduced ambient temperatures and higher power dissipation is permissible, however, provided AC operating parameters are met. See Fig. 1 for derating curve.

- 3 All voltages are referenced to VSS

- 4 Output voltage will swing from V<sub>S</sub> to V<sub>CC</sub> when activated with no current loading For purposes of maintaining data in standby mode, V<sub>CC</sub> may be reduced to V<sub>SS</sub> without affecting refresh operations or data retention. However, the V<sub>OH</sub> (min.) specification is not guaranteed in this mode.

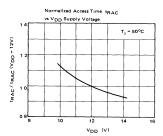

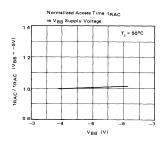

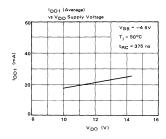

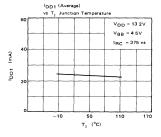

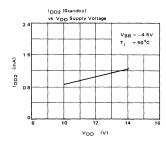

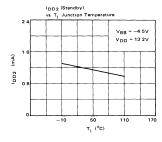

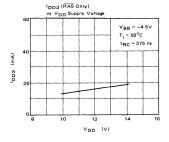

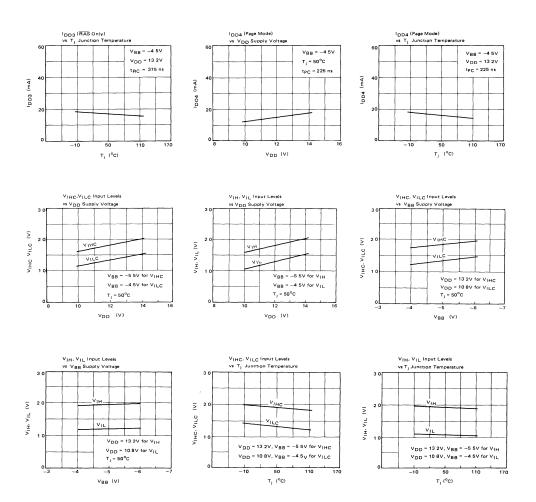

- 5  $I_{DD1}$ ,  $I_{DD3}$  and  $I_{DD4}$  depend on cycle rate See figures 2, 3 and 4 for  $I_{DD}$  limits at other cycle rates

- 6 I<sub>CC1</sub> and I<sub>CC4</sub> depend upon output loading During readout of high level data V<sub>CC</sub> is connected through a low impedance to data out At all other times I<sub>CC</sub> consists of leakage currents only

- 7 After the application of supply voltages or after extended periods of bias (greater than t<sub>REF</sub> 2ms) without clocks, the device must perform about eight initialization cycles prior to normal operation

- 8 AC measurements assume t<sub>T</sub> = 5ns

- 9 The specifications for  $t_{RC}$  (min ),  $t_{RMW}$  (min ) and  $t_{RWC}$  (min ) are used only to indicate cycle time at which proper operation over the full temperature range (0 C  $\lesssim T_a \lesssim 70^{\circ} \text{C}$ ) is assured

- 10 VIHC (min ) or VIH (min ) and VIL (max ) are reference levels for

- measuring timing of input signals. Also, transition times are measured between VIHC or VIH and VIL.

- 111 Assumes that t<sub>RCD</sub> ≤t<sub>RCD</sub> (max) If t<sub>RCD</sub> is greater than the maximum recommended value shown in this table, t<sub>RAC</sub> will increase by the amount that t<sub>RCD</sub> exceeds the value shown

- 12 Assumes that t<sub>RCD</sub> ≥ t<sub>RCD</sub> (max )

- 13 Measured with a load equivalent to 2 TTL loads and 100pF

- 14 t<sub>OFF</sub> (max ) defines the time at which the output achieves the open circuit condition and is not referenced to output voltage levels

- 15 Operation within the t<sub>RCD</sub> (max ) limit insures that t<sub>RAC</sub> (max ) can be met t<sub>RCD</sub> (max ) is specified a reference point only if t<sub>RCD</sub> is greater than the specified t<sub>RCD</sub> (max ) limit, then access time is controlled exclusively by t<sub>CAC</sub>

- These parameters are referenced to CAS leading edge in early write cycles and to WRITE leading edge in delayed write or readmodify-write cycles

- 17 tWCS, tCWD and tRWD are not restrictive operating parameters. They are included in the data sheet as electrical characteristics only.

- If  $t_{WCS} \ge t_{WCS}$  (min ), the cycle is an early write cycle and the data out pin will remain open circuit (high impedance) throughout the entire cycle

- If  $t_{CWD} \ge t_{CWD}$  (min ) and  $t_{RWD} \ge t_{RWD}$  (min ), the cycle is a read-write cycle and the data out will contain data read from the selected cell. If neither of the above sets of conditions is satisfied, the condition of the data out (at access time) is indeterminate.

#### APPLICATION INFORMATION

#### ADDRESSING

The 14 address bits required to decode 1 of the 16,384 cell locations within the TMM416P/D are multiplexed onto the 7 address inputs and latched into the on-chip address latches by externally applying two negative going TTL-level clocks

The first clock, the Row Address Strobe (RAS), latches the 7 row address bits into the chip. The second clock, the Column Address Strobe (CAS), subsequently latches the 7 column address bits into the chip. Each of these signals, RAS and CAS, triggers a sequence of events which are controlled by different delayed internal clocks

The two clock chains are linked together logically in such a way that the address multiplexing operation is done outside of the critical path timing sequence for read data access. The later events in the  $\overline{\text{CAS}}$  clock sequence are inhibited until the occurence of a delayed signal derived from the  $\overline{\text{RAS}}$  clock chain. This "gated  $\overline{\text{CAS}}$ " feature allows the  $\overline{\text{CAS}}$  clock to be externally activated as soon as the Row Address Hold Time specification ( $t_{RAH}$ ) has been satisfied and the address inputs have been changed from Row address to Column address information.

#### DATA INPUT/OUTPUT

Data to be written into a selected cell is latched into an on-chip register by a combination of WRITE and CAS while RAS is active. The later of the signals (WRITE or CAS) to make its negative transition is the strobe for the Data In (DIN) register This permits several options in the write cycle timing. In a write cycle, if the WRITE input is brought low (active) prior to CAS, the DIN is strobed by CAS and the setup and hold times are referenced to CAS If the input data is not available at CAS time or if it is desired that the cycle be a read-write cycle the WRITE signal will be delayed until after CAS has made its negative transition. In this "delayed write cycle" the data input set-up and hold times are referenced to the negative edge of WRITE rather than CAS. (To illustrate this feature, DIN is referenced to WRITE in the timing diagrams depicting the readwrite and page-mode write cycles while the "early write" cycle diagram shows D<sub>IN</sub> referenced to CAS). Data is retrieved from the memory in a read cycle by maintaining  $\overline{WRITE}$  in the inactive or high state throughout the portion of the memory cycle in which  $\overline{CAS}$  is active (low). Data read from the selected cell will be available at the output within the specified access time.

#### DATA OUTPUT CONTROL

The normal condition of the Data Output ( $D_{OUT}$ ) of the TMM416P/D is the high impedance (opencircuit) state. That is to say, anytime  $\overline{CAS}$  is at a high level, the  $D_{OUT}$  pin will be floating. The only time the output will turn on and contain either a logic 0 or logic 1 is at access time during a read cycle.  $D_{OUT}$  will remain valid from access time until  $\overline{CAS}$  is taken back to the inactive (high level) condition

If the memory cycle in progress is a read, readmodify write, or a delayed write cycle, then the data output will go from the high impedance state to the active condition, and at access time will contain the data read from the selected cell. This output data is the same polarity (not inverted) as the input data Once having gone active, the output will remain valid until  $\overline{CAS}$  is taken to the precharge (logic 1) state, whether or not  $\overline{RAS}$  goes into precharge

If the cycle in progress is an "early-write" cycle  $\overline{(WRITE)}$  active before  $\overline{CAS}$  goes active), then the output pin will maintain the high impedance state throughout the entire cycle. Note that with this type of output configuration, the user is given full control of the  $\overline{D_{OUT}}$  pin simply by controlling the placement of  $\overline{WRITE}$  command during a write cycle, and the pulse width of the Column Address Strobe during read operations. Note also that even though data is not latched at the output, data can remain valid from access time until the beginning of a subsequent cycle without paying any penalty in overall memory cycle time (stretching the cycle)

#### PAGE MODE OPERATION

The "Page-Mode" feature of the TMM416P/D allows for successive memory operations at multiple column locations of the same row address with increased speed without an increase in power. This is done by

strobing the row address into the chip and maintaining the  $\overline{\text{RAS}}$  signal at a logic 0 throughout all successive memory cycles in which the row address is common. This "page-mode" of operation will not dissipate the power associated with the negative going edge of  $\overline{\text{RAS}}$ . Also, the time required for strobing in a new row address is eliminated, thereby decreasing the access and cycle times

#### REFRESH

Refresh of the dynamic cell matrix is accomplished by performing a memory cycle at each of the 128 row addresses within each 2 millisecond time interval Although any normal memory cycle will perform the refresh operation, this function is most easily accomplished with "RAS-only" cycles, RAS only refresh results in a substantial reduction in operating power This reduction in power is reflected in the IDD3 specification

#### POWER CONSIDERATIONS

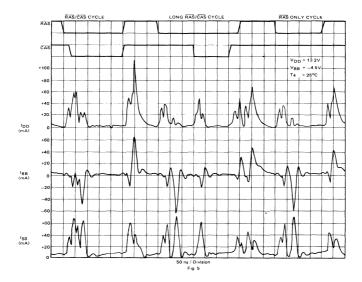

Most of the circuitry used in the TMM416P/D is dynamic and most of the power drawn is the result of an address strobe edge (refer to the TMM416P/D cur-

rent waveforms in Fig 5). In system applications requiring lower power dissipation, the operating frequency (cycle rate) of the TMM416P/D can be reduced and the (guaranteed maximum) average power dissipation of the device will be lowered in accordance with the  $I_{\mbox{\footnotesize DD1}}$  (max ) spec limit curve illustrated in Fig 2

It is possible to operate certain versions of the TMM416P/D family (-2 and 3 speed selections for example) at frequencies higher than specified, provided all AC operating parameters are met. Operation at shorter cycle times (<  $t_{\rm RC}$  min.) results in higher power dissipation and, therefore, a reduction in ambient temperature is required. Refer to Fig. 1 for derating curve

#### POWER UP

The TMM416P/D requires no particular power supply sequencing so long as the Absolute Maximum Rating Conditions are observed. However, in order to insure compliance with the Absolute Maximum Ratings, TOSHIBA recommends sequencing of power supplies such that  $V_{BB}$  is applied first and removed last  $V_{BB}$  should never be more positive than  $V_{SS}$  when power is applied to  $V_{DD}$

#### **TYPICAL CURRENT WAVEFORMS**

#### TYPICAL CHARACTERISTICS

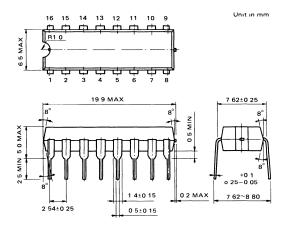

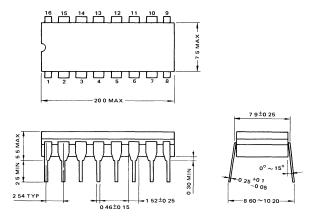

#### **OUTLINE DRAWINGS**

#### Plastic Package

#### Cerdip Package

Note 1 Each lead pitch is 2.54mm. All leads are located within 0.25mm of their true longitudinal position with respect to No. 1 and No. 16 leads

Note Toshiba does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied, and Toshiba reserves the right, at any time without notice, to change said circuitry.

© Feb., 1981 Toshiba Corporation

<sup>2</sup> All dimensions are in millimeters