# MICROCOMPUTER/MICROPROCESSOR PERIPHERAL IC FOR VIEWDATA (LUCY)

The SAA5070 is a complex microcomputer/microprocessor peripheral integrated circuit in N-channel MOS technology intended for use in wired data communication systems, notably viewdata.

#### Features

- Microcomputer/microprocessor interface. Modem both 1200/75 and 1200/1200 baud.

- Line "UART" and tape recorder "UART", both with software parity control (or 8-bit without parity).

- Tape recorder modem (modified 'Kansas City' standard 1300 baud).

- Autodialler for British Post Office and Continental requirements.

- IBUS receivers and transmitters. Timer circuits (60 s and 1.5 s time-outs).

- General input/output ports.

- Provision for connection of any external modem through V24 interface.

#### QUICK REFERENCE DATA

| Supply voltage                      | V <sub>DD</sub> | nom. | 5  | V  |

|-------------------------------------|-----------------|------|----|----|

| Supply current                      | <sup>I</sup> DD | typ. | 75 | mA |

| Operating ambient temperature range | Tamb            | -20  | °C |    |

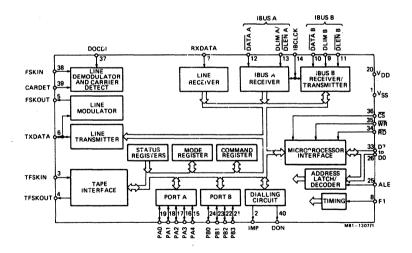

Fig.1a Simplified block diagram

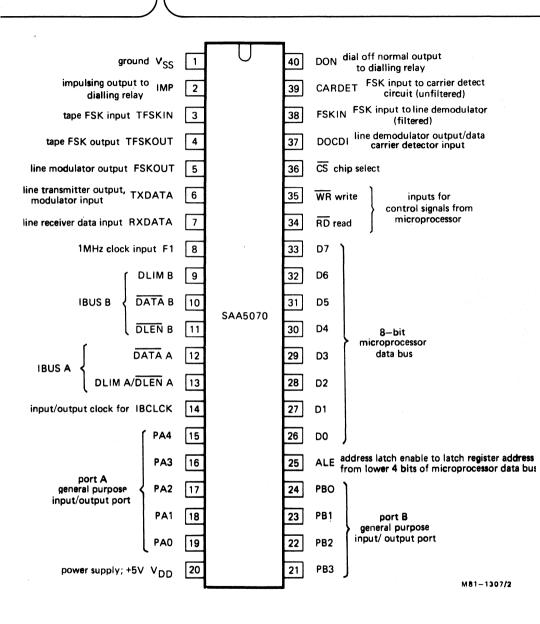

# PACKAGE OUTLINE

40-lead DIL; plastic (SOT-129).

#### Fig.2 Pinning diagram

344

#### DESCRIPTION

The SAA5070 is a 40 pin integrated circuit in N-channel MOS with a 1 MHz clock supplying all the operating frequencies. It performs most of the hardware functions of a viewdata terminal including an autodialling circuit, a 1200 baud demodulator and asynchronous receiver, and a 75/1200 baud modulator and asynchronous transmitter.

The device also includes a tape interface circuit suitable for the recording of character codes of pages of text on a standard audio cassette recorder, and an IBUS receiver and receiver/transmitter on separate ports enabling the software recoding of IBUS transmissions. The 75 baud modulator and asynchronous transmitter can be switched to operate at 1200 baud for private telecommunications systems.

There are also two general purpose input/output ports. Port A could, for example, be used as an interface to a non volatile RAM which can store telephone numbers for autodialling and user passwords and Port B could be used for display control.

The SAA5070 has been partitioned for flexibility of use, e.g. an external modem can be used, if required, in conjunction with the internal asynchronous receiver and transmitter, or the internal modem can be used independently of the internal receiver and transmitter. Also the tape interface can work independently of, and simultaneously with, the line receiver.

#### HANDLING

Inputs and outputs are protected against electrostatic charge in normal handling. However, to be totally safe, it is desirable to take normal precautions appropriate to handling MOS devices. (See 'HANDLING MOS DEVICES').

RATINGS Limiting values in accordance with the Absolute Maximum System (IEC134).

| Voltages (with respect to pin 1)                                                                                 |                  | min. | typ.  | max.    |    |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------|------------------|------|-------|---------|----|--|--|--|--|

| Supply voltage (pin 20)                                                                                          | V <sub>DD</sub>  | 0.3  |       | 7.5     | V  |  |  |  |  |

| Input voltage:                                                                                                   |                  |      |       |         |    |  |  |  |  |

| PORT A (pins 15 to 10) and PB0 (pin 24)                                                                          | VI               | -0.3 | -     | 14.0    | V  |  |  |  |  |

| Input voltage (all other pins)                                                                                   | VI               | 0.3  |       | 7.5     | V  |  |  |  |  |

| Temperatures                                                                                                     |                  |      |       |         |    |  |  |  |  |

| Storage temperature range                                                                                        | T <sub>stq</sub> |      | -20 1 | to +125 | oC |  |  |  |  |

| Operating ambient temperature range                                                                              | Tamb             |      | -20   | to +70  | oC |  |  |  |  |

| CHARACTERISTICS                                                                                                  |                  |      |       |         |    |  |  |  |  |

| Supply voltage (pin 20)                                                                                          | V <sub>DD</sub>  | 4.5  |       | 5.5     | V  |  |  |  |  |

| The following characteristics apply at $T_{amb}$ = 25 <sup>o</sup> C and $V_{DD}$ = 5 V unless otherwise stated. |                  |      |       |         |    |  |  |  |  |

| Supply current                                                                                                   | DD               |      | 75    | 150     | mA |  |  |  |  |

| Inputs                                                                                                           |                  |      |       |         |    |  |  |  |  |

| All inputs (except F1 clock)                                                                                     |                  |      |       |         |    |  |  |  |  |

| Input voltage; LOW                                                                                               | VIL              | -0.3 |       | 0.8     | V  |  |  |  |  |

| Input voltage; HIGH                                                                                              | VIH              | 2.0  |       | 5.5     | V  |  |  |  |  |

| Input leakage current (V <sub>1</sub> = 0 to 5.5 V)                                                              | <sup>I</sup> IR  | _    |       | 10      | μA |  |  |  |  |

| Input capacitance                                                                                                | Cl               | _    |       | 7       | рF |  |  |  |  |

Data specific to certain inputs

|                                                                       |                   | min.         | typ.  | max.  |     |

|-----------------------------------------------------------------------|-------------------|--------------|-------|-------|-----|

| F1 (1 MHz) Clock                                                      |                   |              |       |       |     |

| Input voltage; LOW                                                    | VIL               | 0.3          | -     | 0.6   | V   |

| Input voltage; HIGH                                                   | VIH               | 2.2          |       | 5.5   | v   |

| Input leakage current ( $V_1 = 0$ to 5.5 V)                           | IIR               |              | -     | 10    | μA  |

| Input capacitance                                                     | CI                | · <u>-</u> · | -     | 7     | рF  |

| Mark/space ratio (measured at 1.5 V level)                            |                   | 40:60        | · _ · | 60:40 |     |

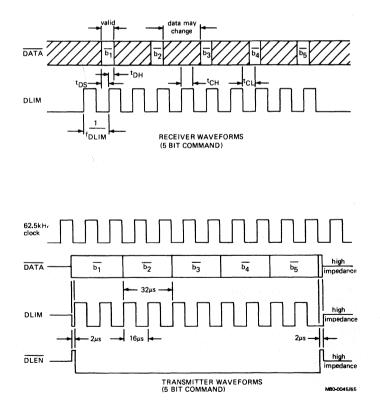

| DATA A, DLIM A/DLEN A (IBUS A)                                        |                   |              |       |       |     |

| Data set up time                                                      | tDS               | 3            |       |       | μs  |

| Data hold time                                                        | <sup>t</sup> DH   | 3            | -     |       | μs  |

| DLIM clock; HIGH                                                      | <sup>t</sup> CH   | 4            |       |       | μs  |

| DLIM clock; LOW                                                       | <sup>t</sup> CL   | 4            | -     | 62    | μs  |

| Time between commands                                                 | <sup>t</sup> BC   | 140          | -     | ~     | μs  |

| DLIM frequency                                                        | <sup>f</sup> DLIM | 16           |       | 160   | kHz |

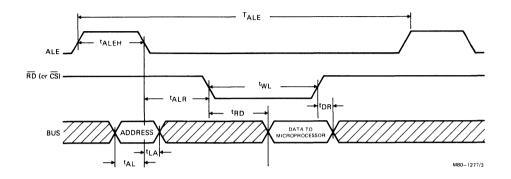

| ALE (Address Latch Enable) (Figs. 3 and 4)                            |                   |              |       |       |     |

| Pulse width (HIGH)                                                    | <sup>t</sup> ALEH | 400          | -     | _     | ns  |

| Cycle time                                                            | TALE              | -            | 2500  |       | ns  |

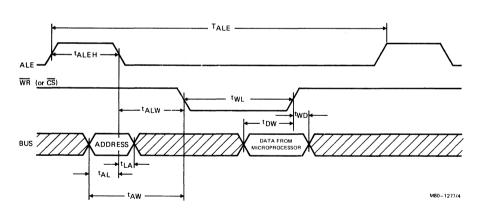

| $\overline{RD}$ , $\overline{WR}$ and $\overline{CS}$ (Figs. 3 and 4) |                   |              |       |       |     |

| Control pulse width                                                   | twl               | -            | 700   | -     | ns  |

| Address hold time                                                     | <sup>t</sup> LA   | 80           | ·     | -     | ns  |

| Address set-up time                                                   | <sup>t</sup> AL   | 120          |       |       | ns  |

| Read cycle timings (Fig.3)<br>ALE to read pulse delay time            | <sup>t</sup> ALR  | 80           | -     | _     | ns  |

| Read pulse (falling edge)<br>to data bus delay time                   | tRD               | _            |       | 500   | ns  |

| Data hold time                                                        | <sup>t</sup> DR   | 0            |       | 200   | ns  |

| Write cycle timings (Fig.4)                                           | -011              | -            |       |       |     |

| ALE to write pulse delay time                                         | <sup>t</sup> ALW  | 80           | -     |       | ns  |

| Address set-up time to $\overline{WR}$                                | <sup>t</sup> AW   | 230          |       |       | ns  |

| Data set up time before WR                                            | tDW               | 500          | _     | -     | ns  |

| Data hold time after WR                                               | twd               | 120          | · -   |       | ns  |

|                                                                       |                   |              |       |       |     |

Fig.3 Read cycle timing

Fig.4 Write cycle timing

| Inputs/( | Outputs |

|----------|---------|

|----------|---------|

These are protected against connection to  $V_{SS}$  or  $V_{DD}$

|                                                                                 | )           | min.                                 | typ.          | max.             |      |    |

|---------------------------------------------------------------------------------|-------------|--------------------------------------|---------------|------------------|------|----|

| DATA B, DLIM B, DLEN B, IBCLCK (IBU                                             | JS B)       |                                      |               | .,p.             |      |    |

| Input voltage; LOW                                                              | 1           | VIL                                  | -0.3          | -                | 0,8  | V  |

| Input voltage; HIGH                                                             |             | VIH                                  | 2.0           |                  | 5.5  | V  |

| Input leakage current (V <sub>I</sub> = 0 to 5.5 V)<br>(3 state buffers off)    | Fig.14      | IIR                                  |               |                  | 10   | μA |

| Input capacitance                                                               | F 19.14     | CI                                   | -             | -                | 7    | рF |

| Output voltage; LOW (I <sub>OL</sub> = 1.6 mA)                                  |             | VOL                                  | -             |                  | 0.4  | v  |

| Output voltage; HIGH ( $-I_{OH} = 200 \ \mu A$ )                                |             | v <sub>он</sub>                      | 2.4           |                  |      | v  |

| Output rise and fall times ( $C_L = 300 \text{ pF}$ )                           | I           | t <sub>r</sub> ∣<br>t <sub>f</sub> ∫ |               | -                | 1    | μs |

| other timings as IBUS A                                                         |             |                                      |               |                  |      |    |

| DOCDI (open drain output)                                                       |             |                                      |               |                  |      |    |

| Input voltage; LOW                                                              |             | VIL                                  | 0.3           |                  | 0.8  | v  |

| Input voltage; HIGH                                                             |             | VIH                                  | 2.0           | -                | 5.5  | v  |

| Input leakage current; (V <sub>1</sub> = 0 to 5.5 V)<br>(output transistor off) |             | IIR                                  | _             | 0.4              | 10   | μA |

| Input capacitance                                                               |             | CI                                   | -             |                  | 7    | рF |

| Output voltage; LOW (I <sub>OL</sub> = 1.6 mA)                                  |             | VOL                                  | -             | 0.4              | -    | v  |

| TXDATA                                                                          |             |                                      |               |                  |      |    |

| (Internal resistive pull-up, permitting wired                                   | l - AND con | nection)                             |               |                  |      |    |

| Input voltage; LOW                                                              |             | VIL                                  | -0.3          | _                | 0.8  | v  |

| Input voitage; HIGH                                                             |             | VIH                                  | 2.0           |                  | 5.5  | V  |

| Input current; LOW ( $V_1 = 0.4 V$ )                                            |             | -11L                                 | _             |                  | 500  | μA |

| Input capacitance                                                               |             | CI                                   |               |                  | 7    | рF |

| Output voltage; LOW (I <sub>OL</sub> = 1.6 mA)                                  |             | VOL                                  |               |                  | 0.4  | v  |

| Output voltage; HIGH ( $-I_{OH} = 50 \mu A$ )                                   |             | v <sub>он</sub>                      | 2.4           |                  | -    | V  |

| Load capacitance                                                                |             | сL                                   |               | ° <u>–</u> 1     | 40   | рF |

| Output rise time ( $C_L = 40 \text{ pF}$ )                                      |             | t <sub>r</sub>                       |               | 3                | -    | μs |

| PA0 to PA4 (PORT A) (open drain output                                          | t)          |                                      |               |                  |      |    |

| Input voltage; LOW                                                              |             | VIL                                  | -0.3          |                  | 0.8  | V  |

| Input voltage; HIGH                                                             |             | VIH                                  | 2.0           | - , <sup>,</sup> | 13.2 | V  |

| Input capacitance                                                               |             | CI                                   | -             |                  | 7    | pF |

| Output voltage; LOW (I <sub>OL</sub> = 1.6 mA)                                  |             | VOL                                  | , <del></del> |                  | 0.4  | V  |

| Off state leakage current ( $V_1 = 0$ to 13.2 V                                 | )           | IOR                                  |               |                  | 10   | μA |

| Load capacitance                                                                |             | CL                                   |               |                  | 40   | рF |

| Fall time                                                                       |             | tf                                   |               | -                | 1    | μs |

#### Microcomputer/microprocessor peripheral IC for viewdata

| - |                                                                              |                 |      |      |      |         |

|---|------------------------------------------------------------------------------|-----------------|------|------|------|---------|

|   | Inputs/Outputs (continued)                                                   |                 | min. | typ. | max. |         |

|   | PBO (PORT B) (open drain output) as PORT A except                            | :               |      |      |      |         |

|   | Output voltage; LOW (I <sub>OL</sub> = 1.6 mA)                               | VOL             |      | -    | 0.4  | v       |

|   | Output voltage; HIGH                                                         | VOH             |      |      | 13.2 | V       |

|   | Load capacitance                                                             | CL              |      | -    | 100  | рF      |

|   | PB1 to PB3 (PORT B)                                                          |                 |      |      |      |         |

|   | Input voltage; LOW                                                           | VIL             | -0.3 | -    | 0.8  | v       |

|   | Input voltage; HIGH                                                          | VIH             | 2.0  | -    | 5.5  | V       |

|   | Input capacitance                                                            | CI              |      | -    | 7    | рF      |

|   | Load capacitance                                                             | CL              | _    | -    | 100  | рF      |

|   | Output voltage; LOW (I <sub>OL</sub> = 1.6 mA)                               | VOL             | -    |      | 0.4  | V       |

|   | Off state leakage current ( $V_1 = 0$ to 5.5 V)                              | IOR             | -    | -    | 10   | μA      |

|   | D0 to D7 (8-bit Data bus)                                                    |                 |      |      |      |         |

|   | Input voltage; LOW                                                           | VIL             | -0.3 | -    | 0.8  | V       |

|   | Input voltage; HIGH                                                          | VIH             | 2.0  | -    | 5.5  | V       |

|   | Output voltage; LOW (I <sub>OL</sub> = 1.6 mA)                               | VOL             |      | -    | 0.4  | V       |

|   | Output voltage; HIGH ( $-I_{OH} = 200 \ \mu A$ )                             | V <sub>OH</sub> | 2.4  | -    | -    | V       |

|   | Input leakage current (V <sub>I</sub> = 0 to 5.5 V)                          |                 |      |      |      |         |

|   | (3-state buffers off)                                                        | <sup>I</sup> IR |      | -    | 10   | μA      |

|   | Input capacitance                                                            | CI              |      | -    | 7    | рF      |

|   | Output rise and fall times ( $C_L = 150 \text{ pF}$ )                        | t <sub>r</sub>  |      | -    | 150  | ns      |

|   | Outputs                                                                      |                 |      |      |      |         |

|   | These are protected against connection to V <sub>SS</sub> or V <sub>DD</sub> |                 |      |      |      |         |

|   | FSKOUT and TFSKOUT                                                           |                 |      |      |      |         |

|   | Output voltage; LOW (I <sub>OL</sub> = 1.6 mA)                               | VOL             |      | -    | 0.4  | V       |

|   | Output voltage; HIGH ( $-I_{OH} = 200 \ \mu A$ )                             | V <sub>OH</sub> | 2.4  |      | _    | V       |

|   | Rise and fall times ( $C_L = 100 \text{ pF}$ )                               | tr              | _    | _    | 500  | ns      |

|   |                                                                              | tf              |      |      |      |         |

|   | DON and IMP                                                                  | N/              |      |      | 0.2  | v       |

|   | Output voltage; LOW ( $I_{OL} = 50 \mu A$ )                                  | VOL             | -    | -    | 2000 |         |

|   | Output current; HIGH ( $V_{OH} = 0.8 \text{ V clamped}$ )*                   | <sup>I</sup> OH | 200  | _    | 2000 | μA<br>V |

|   | Output voltage; HIGH $(-I_{OH} = 200 \ \mu \text{A})$                        | VOH             | 2.4  | _    | _    | v       |

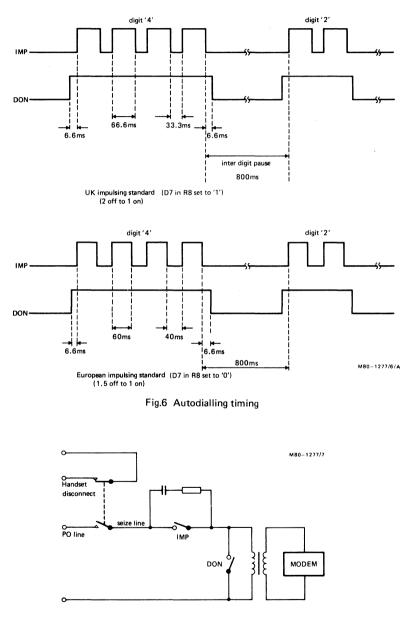

|   | Autodialling timings are given in Fig.6                                      |                 |      |      |      |         |

\*These outputs are normally intended to drive the base-emitter junction of a bipolar transistor and so in normal use the  $V_{OH}$  may be clamped to  $V_{be}$ .

#### RESET FUNCTION

It is possible to reset the SAA5070 to its nominal state either automatically on power-on by means of an internal power-on reset circuit, or by setting D5 in command register (R3) to '1', which returns to '0' on completion of the reset sequence. The device resets to viewdata mode, i.e. 75 baud transmit rate, even parity, etc, as shown by the all zero's state in registers R0 to R3, R6, R7 and R8 except for LTXRDY, IBTXRDY, and TTXRDY (in the status registers R0 and R1) which will come up as '1' after the transmitters have been reset, showing that they are ready to accept new data.

```

June 1981

```

#### APPLICATION DATA

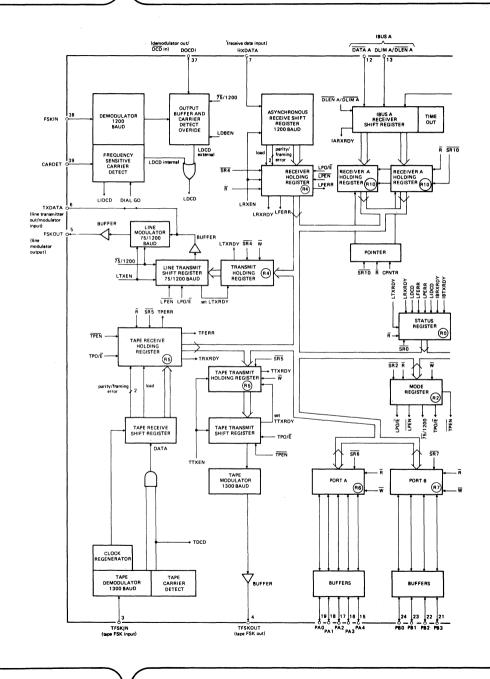

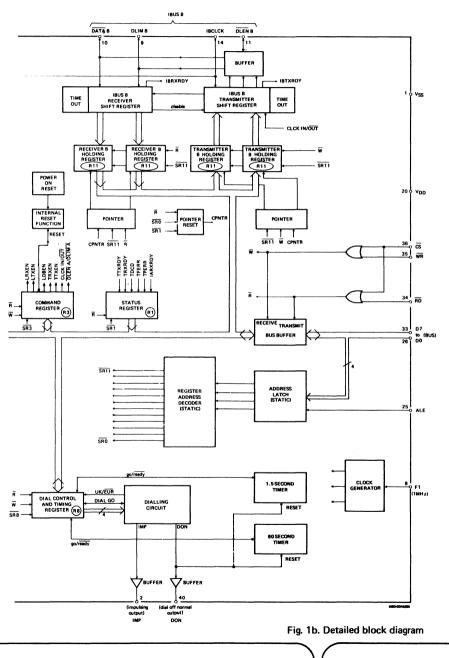

#### Chip organisation

Each section of the SAA5070 may be accessed by the microprocessor via a register (of up to 8-bits) connected to an internal data bus. There are 15 registers on chip accessed by 11 addresses. Some of the registers are two-level, i.e. two bytes of data are transferred by two successive read (or write) sequences to the same address, also some read only registers have the same address as a write only register.

An appendix lists the registers, their contents, and their use.

#### Section descriptions

The description of each section includes associated registers, flags, and pins, as well as the method of operation. On the following block diagrams external pins are shown boxed and internal flags are shown underlined.

#### **Microprocessor Interface**

| D0 to D7 –       | I/O | <ul> <li>8-bit input/output port</li> </ul> |                                          |  |

|------------------|-----|---------------------------------------------|------------------------------------------|--|

| Associated pins: | ALE | input                                       | address latch enable from microprocessor |  |

|                  | WR  | input                                       | write pulse from microprocessor          |  |

|                  | RD  | input                                       | read pulse from microprocessor           |  |

|                  | CS  | input                                       | chip select                              |  |

#### Operation

The control microprocessor communicates with the SAA5070 via an 8-bit data I/O port D0 to D7. An internal read or write pulse is produced by gating  $\overline{RD}$  and  $\overline{WR}$  with  $\overline{CS}$ . A single register is enabled onto the internal bus by gating the read or write lines with the address decoder outputs. The register address is taken from the 4 least significant data bits latched on the falling edge of ALE. (See timing diagrams Figs. 3, 4). The address (D3 most significant, D0 least significant) relates directly to the register numbers shown in the register map, detailed in the appendix, and referred to in other section descriptions.

Four registers not specifically related to any one section are included. These are the status registers R0 and R1, the mode register R2, and the command register R3. These registers are used to determine the current status of the device, to dictate the mode of operation or to initiate a specific operation. The status registers are read only, the mode and command registers are read/write. When writing to these registers, it is recommended that the unallocated bits are set to '0'. On reading the registers the state of the unallocated bits should be assumed to be random. The exact functions of the flags contained in these registers are described in the section description to which they relate.

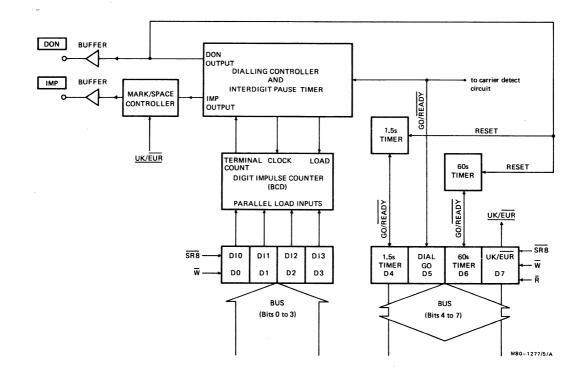

Autodial section (see Fig.5)

Associated Register: - R8 - D0 to D3 write only D4 to D7 read/write

Associated flags in other registers: None

Associated pins: DON output to drive dialling relays

#### Operation

The autodial section includes a clock divider, a digit impulse counter, a sequence controller and an impulse generator (see block diagram Fig.5). A sequence to generate the impulses for one digit is initiated by setting D5 (DIAL GO) to '1', D3 to D0 to the binary code of the required digit, and D7 to the required mode. This initiates the sequence controller which loads the binary code into the digit impulse counter. The counter the generates the correct number of impulses at the rate of 10 per second, together with a DON pulse which overlaps the impulses by about 7 ms at the start and end (see Figs.6, 7); the interdigit pause period is also added by the sequence controller. D5 is reset to '0' at the end of a dialling sequence and may be read by the microprocessor to determine when the dial circuit is free to accept the next digit.

D7 (UK/ $\overline{EUR}$ ) determines the mark/space ratio of the IMP pulses UK = 2 off to 1 on  $\overline{EUR}$  = 1.5 off to 1 on both one pulse per 100 ms

There is a timer in the dial circuit which can be used to time out 1.5 seconds or 60 seconds by setting D4 or D6 respectively. These bits are read/write and are reset after the relevant time out period. In addition the 60 second timer can be reset by writing a '0' to D6. The 60 second timer may be used typically by the microprocessor to release the telephone line if connection has not been made within 60 seconds. The DON pulse resets the counter so that the time out is taken from the end of the last digit dialled. Once a dialling sequence for one digit has been initiated, R8 should be used only in read mode until D5 has been reset internally to '0' indicating the end of the dial sequence for that digit.

When D5 (DIAL GO) is set to '1' the carrier detect circuit (see the next section and Fig.8) is disabled.

Fig.5 Autodial block diagram

352

SAA5070

Fig.7 Simplified relay diagram

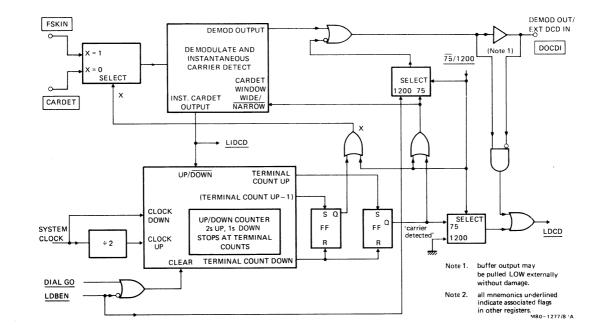

Line Demodulator and Carrier Detect (see Fig.8) Associated Register:- None Associated flags in other registers:

|              |       | D2                    | -  | RU (Status)                          | _   | instantaneous carrier detect flag                                                                          |

|--------------|-------|-----------------------|----|--------------------------------------|-----|------------------------------------------------------------------------------------------------------------|

| LDCD         | -     | D5                    | -  | R0 (Status)                          | -   | carrier detect flag                                                                                        |

| 75/1200      |       | D5                    |    | R2 (Mode)                            |     | transmit frequency baud rate (used in demodulator carrier detect circuit)                                  |

| LDBEN        | -     | D4                    |    | R3 (Command)                         |     | line demodulator output buffer and carrier detect enable                                                   |

| DIAL GO      | -     | D5                    | -  | R8 (Dial control)                    | -   | used to disable carrier detect circuit during<br>dialling sequence                                         |

| Associated ( | oins: | FSKIN<br>CARD<br>DOCD | ΕT | — input<br>— input<br>— input/output | — u | ltered, squared F.S.K. signal<br>nfiltered (squared) F.S.K. signal.<br>emodulator output, external LDCD in |

instantaneous carrier detect flag

#### Operation

The input to the demodulator is the previously filtered and squared up F.S.K. signal from the telephone line. Its output is a pseudo analogue signal which must be externally filtered and squared to produce the demodulated data. The carrier detect circuit functions in the following modes:

a) Viewdata mode (1200 baud receive, 75 baud transmit). Initially, a narrow frequency band 'window' around 1300 Hz is accepted as carrier, this must be applied to the CARDET input. If a frequency in this range is present, the 'instantaneous carrier detected' flag will be HIGH (LIDCD), after about 2 seconds the 'line carrier detected' flag will be set HIGH (LDCD). When this occurs, the frequency window is widened to include 2100 Hz and the circuit no longer takes its input from the CARDET pin, but from the FSKIN pin.

If carrier is then removed LIDCD immediately goes LOW, and after about 1 second LDCD is reset, the frequency window again becomes narrow and around 1300 Hz and the CARDET input again, becomes active. Reappearance of carrier in the 1300 Hz range will cause a repeat of the above.

b) 1200 baud each way mode

Only the instantaneous carrier detect is active in this mode. LDCD is forced LOW and the CARDET input inhibited (only FSKIN should be used in this mode).

c) External carrier detect input

If an external modem is used its (active LOW) carrier detect output is connected to DOCDI. Provided that the demodulator is not enabled, LDCD will be set if DOCDI is LOW and reset if it is HIGH.

#### Demodulator enable

LDCD is produced by the carrier detect circuit, which is enabled by LDBEN and disabled by DIAL GO, In the viewdata mode the demodulator is enabled by LDCD.

In the 1200 baud each way mode the demodulator is enabled directly by LDBEN.

Fig.8 Line demodulator and carrier detect block diagram

$\mathcal{T}$

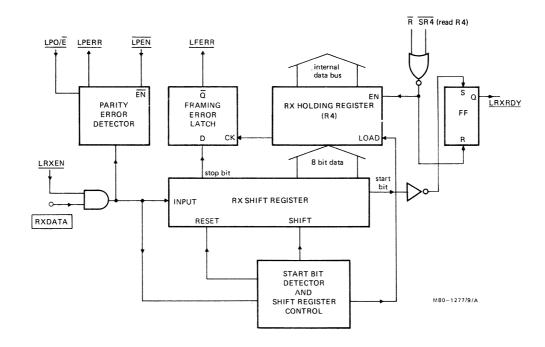

Line Receiver (see Fig.9) Associated Register: – R4 read only Associated flags in other registers:

| LRXRDY                  | <del></del> | D6 | ÷                             | RO (status)  |   | valid data available in receive holding register       |  |

|-------------------------|-------------|----|-------------------------------|--------------|---|--------------------------------------------------------|--|

| LFERR                   | -           | D4 | -                             | RO (status)  | - | line framing error (derived from STOP bit of message). |  |

| LPERR                   | _           | D3 | -                             | RO (status)  | - | line parity error.                                     |  |

| LPO/E                   | -           | D7 | -                             | R2 (mode)    |   | odd or even parity detection mode select               |  |

| LPEN                    | -           | D6 | -                             | R2 (mode)    | - | 8 bit data or 7 bit plus parity mode select            |  |

| LRXEN                   |             | D7 | <del></del>                   | R3 (command) | - | line receiver enable.                                  |  |

| Associated pins: RXDATA |             |    | - input - received data input |              |   |                                                        |  |

#### Operation

The receiver may be configured to work with either 7 data bits and 1 parity, or with 8 data bits and no parity. Odd or even parity can be detected on chip, the LPERR flag being set when an error is detected. The required mode of operation should be selected by setting LPEN and LPO/E to the required states by writing to mode register (R2) before enabling the receiver by setting LRXEN to '1' in command register (R3). The data format is 10 bits per data word. The data word is made up of a start bit (LOW), 8 data bits, the 8th being an optional parity bit, and a stop bit (HIGH). The receive data will remain HIGH after the stop bit until the next data word. When the receiver has been enabled a negative transition is looked for on the RXDATA input indicating a possible start bit. After half a bit rate period the data is sampled again and if it is still LOW it is interpreted as a start bit, initiating a sequence which clocks the data into a shift register. When the full ten bit message has been received, the 8 data bits are parallel loaded into the receiver holding register (R4), the LRXRDY flag is set to '1'. The complement of the stop bit is loaded into the LFERR latch and the result of the parity check is loaded into LPERR latch. If line parity is not enabled i.e. LPEN = '1', then LPERR is held at '0'. The LRXRDY flag is reset to '0' after the microprocessor has read the receiver holding register (R4). The receiver has a 52 times baud rate factor to allow for maximum isochronous distortion.

#### **DEVELOPMENT DATA**

SAA5070

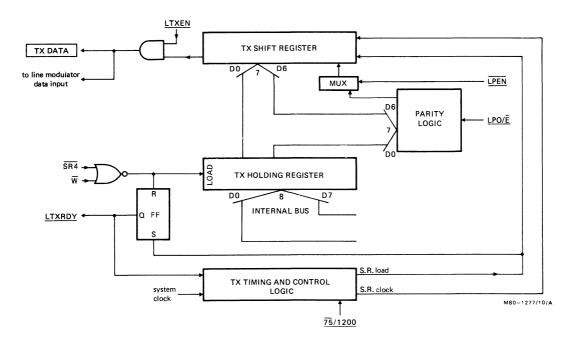

Line Transmitter (see Fig.10) Associated Register: – R4 write only Associated flags in other registers:

| LTXRDY     | -     | D7     | R0 (status)  | <ul> <li>transmit holding register ready to accept new<br/>data</li> </ul> |

|------------|-------|--------|--------------|----------------------------------------------------------------------------|

| LPO/E      | _     | D7 —   | R2 (mode)    | <ul> <li>odd or even parity mode select</li> </ul>                         |

| LPEN       |       | D6 —   | R2 (mode)    | <ul> <li>8 bit data or 7 bit data with parity mode<br/>select</li> </ul>   |

| 75/1200    | -     | D5 —   | R2 (mode)    | <ul> <li>select transmit baud rate</li> </ul>                              |

| LTXEN      | -     | D6 –   | R3 (command) | <ul> <li>line transmitter/modulator output enable</li> </ul>               |

| Associated | pins: | TXDATA | A – I/O –    | transmitter output (and also modulator input)                              |

#### Operation

The data format of the transmitter is the same as that of the line receiver <u>i.e. 10</u>-bits, a start bit (LOW) followed by 8-data bits, the 8th bit being an optional parity (selected by LPEN), odd or even parity being selectable (by LPO/ $\overline{E}$ ) ending with a STOP bit (HIGH) the output remaining HIGH until the next data word is written.

The transmitter and modulator may be used together or separately. The transmitter output is brought to the TXDATA pin (if LTXEN = 1) which is connected internally to the modulator input. The TXDATA pin has an internal resistive pull up permitting wire - AND connection. If the modulator is used with an off chip data source (e.g. UART) then data should not be written to the internal transmit holding register (R4). The STOP bit (HIGH) will then be continuously output when LTXEN = 1 (required to enable modulator output) allowing the external UART to control the TXDATA (pin 6).

To operate the transmitter the required mode should be set-up initially by writing to the mode register (R2) the required states of  $\overline{75}/1200$ , LPEN, LPO/E. The transmitter can then be enabled by setting LTXEN to '1' in the command register (R3). The 8-bit data word can then be written to the transmit holding register (R4). If parity is enabled then the 8th bit is ignored and the value of the parity bit calculated from the first 7-data bits and LPO/E. The LTXRDY flag is set to zero when the holding register is written into. If the transmit output shift register is not currently in use the contents of the holding register are transferred to the output shift register and LTXRDY returns to '1'. This means that new data may now be written to the holding register but will not be transferred to the output shift register with the data word automatically.

Two transmit baud rates are selectable, 75 baud for viewdata transmissions or 1200 baud for private data communication systems.

DEVELOPMENT DATA

SAA5070

359

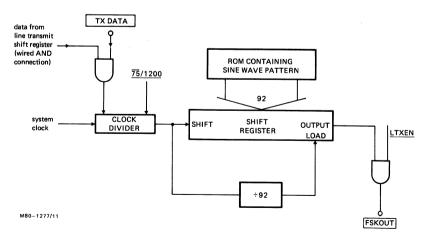

| Line Modulator (see Fig.11)          |      |                  |        |               |   |                                                                               |  |  |  |

|--------------------------------------|------|------------------|--------|---------------|---|-------------------------------------------------------------------------------|--|--|--|

| Associated Register: – None          |      |                  |        |               |   |                                                                               |  |  |  |

| Associated flags in other registers: |      |                  |        |               |   |                                                                               |  |  |  |

| 75/1200                              |      | D5 —             | R2 (m  | ode)          | - | transmit baud rate select.                                                    |  |  |  |

| LTXEN                                | -    | D6 —             | R3 (cc | ommand)       |   | line transmitter/modulator output enable.                                     |  |  |  |

| Associated Pi                        | ins: | TXDATA<br>FSKOUT |        | I/O<br>output | - | modulator input (also (on chip) transmitter output).<br>line modulator output |  |  |  |

#### Operation

The modulator generates a pseudo analogue signal from a serial shift register which is parallel loaded with patterns from an internal ROM. The frequency of the sine wave is determined by the selected baud rate  $\overline{75}/1200$ , and the value of the data on TXDATA (pin 6).

| data      | '1'     | Ό'      |

|-----------|---------|---------|

| 1200 baud | 1300 Hz | 2100 Hz |

| 75 baud   | 390 Hz  | 450 Hz  |

One sine wave cycle is comprised of a 92-bit pattern which after minimal external low pass filtering provides a suitable F.S.K. signal out (see Fig.11)

| Tape section<br>Associated rec |       | Ŭ      |            | transm                 | nit ho | two registers with the same address:<br>Iding register write only<br>ding register read only |

|--------------------------------|-------|--------|------------|------------------------|--------|----------------------------------------------------------------------------------------------|

| Associated fla                 | igs i | in otł | ner re     | gisters:               |        |                                                                                              |

| TTXRDY -                       | -     | D7     |            | R1 (status)            |        | transmit holding register ready to accept new data                                           |

| TRXRDY -                       | -     | D6     |            | R1 (status)            |        | valid data available in receive holding register                                             |

| TDCD -                         | -     | D5     | -          | R1 (status)            | -      | tape data carrier detect flag                                                                |

| TFERR -                        | -     | D4     |            | R1 (status)            |        | tape framing error (derived from STOP bit of message)                                        |

| TPERR -                        | -     | D3     | -          | R1 (status)            |        | tape parity error                                                                            |

| TPO/E -                        | -     | D3     | -          | R2 (mode)              |        | odd or even parity mode select.                                                              |

| TPEN -                         | -     | D2     |            | R2 (mode)              |        | 8-bit data or 7-bit plus parity mode select                                                  |

| TRXEN -                        | -     | D3     |            | R3 (command)           | _      | tape receiver enable                                                                         |

| TTXEN -                        | -     | D2     | -          | R3 (command)           |        | tape transmitter enable                                                                      |

| Associated pir                 | ns:   |        | KIN<br>KOU | — input<br>IT — output | -      | F.S.K. input to tape sections<br>F.S.K. modulated data out                                   |

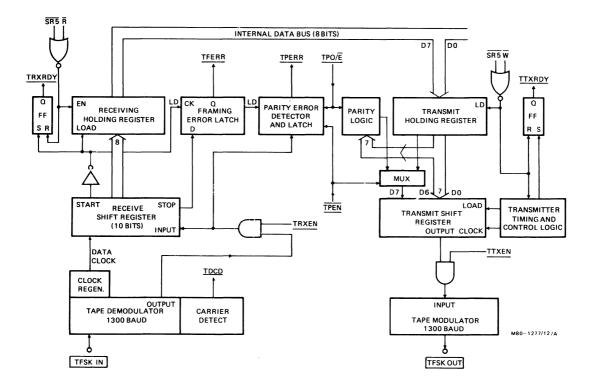

#### Operation of tape section (see Fig.12)

The tape data modulation system is a modified form of the 'Kansas City' standard. A logic '1' is represented by one cycle of 1300 Hz, and a logic '0' by two cycles of 2600 Hz, the data rate being 1300 baud. The data format is the same as that for viewdata, i.e. 10-bit words consisting of a START bit (LOW), followed by 8-data bits, the 8th being an optional parity bit, ending with a STOP bit (HIGH) which is continuous until the next data word.

To operate the tape section the required parity mode should first be set up by writing the required states of TPEN and TPO/ $\vec{E}$  to the mode register (R2). The TTXEN command enables the output of the transmit shift register into the modulator, and should be set before data is written to the transmit holding register. (With TTXEN = '0' the modulator outputs a continuous 1300 Hz signal '1'). When a data word is written to the transmit holding register the TTXRDY flag is reset to '0'. If the transmit shift register is not currently active the contents of the holding register, along with valid parity bit (if enabled) and the START and STOP bits are transferred to the transmit shift register or 1'. The holding register is then free to accept new data but this will not be transferred to the shift register until the current data has been clocked out. Data should be written to the tape transmit holding register, therefore, only when TTXRDY = '1'.

The modulator produces 1300 Hz and 2600 Hz signals which occur synchronously with the data from the transmitter. Hence a '1' is one complete 1300 Hz cycle, and a '0' two complete 2600 Hz cycles. The modulator output, TFSKOUT, requires minimal external low pass filtering to produce data suitable for audio cassette tape recorders.

To overcome the tendency of cassette recorders to attenuate high frequencies, the 1300 Hz signal contains 2  $\mu$ s wide attenuating pulses every 12  $\mu$ s. This reduces the 1300 Hz signal by approximately 3 dB relative to the 2600 Hz signal after external filtering.

The data rate of 1300 baud is slightly faster than the 1200 baud line receive rate, allowing incoming data from the line to be transferred simultaneously (via the microprocessor) to tape.

The TFSKIN input accepts the previously filtered and squared data from the tape recorder. The demodulator uses the fact that the modulated data is in phase with clock to regenerate the clock from the data. This permits a wide tolerance on replay speeds. A carrier detect circuit is included which sets the TDCD flag to '1' if carrier (1300 Hz or 2600 Hz) is valid for 100 ms. If carrier is lost for 100 ms the TDCD flag is reset to '0'. This flag may be read by the microprocessor to determine when to enable the tape receiver by setting TRXEN to '1'.

If TRXEN is set, then on detection of a start bit (LOW) data is shifted into the tape receive shift register by the clock which has been extracted from the data. After ten clocks, the contents of the shift register are transferred to the receive holding register. At the same time the complement of the STOP bit is loaded into the TFERR latch, the results of the parity calculation loaded into the TPERR latch, and TRXRDY is set to '1'. The TRXRDY flag is read by the microprocessor to identify when valid data is in the holding register and is reset to '0' when the holding register (R5) is read. **DEVELOPMENT DATA**

SAA5070

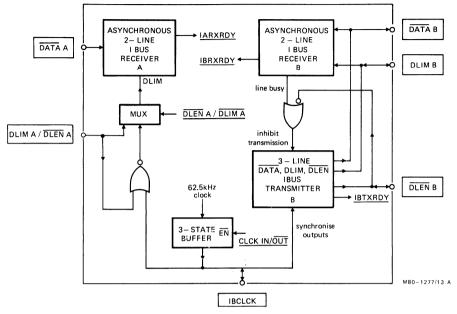

IBUS A receiver and IBUS B receiver/transmitter (see Fig.13)

| Associated registers:  |      |         |      |                                                                       |

|------------------------|------|---------|------|-----------------------------------------------------------------------|

| Receiver A (2 bytes)   |      |         | R1   | 0 — read only                                                         |

| Receiver B (2 bytes)   |      |         | R1   | 1 — read only                                                         |

| Transmitter B (2 byt   | es)  |         | R1   | 1 — write only                                                        |

| Associated flags in or | ther | registe | ers: |                                                                       |

| IBRXRDY                |      | D1      | _    | R0 (status) – valid data available in receiver B holding register     |

| IBTXRDY                | _    | D0      |      | R0 (status) – transmitter B holding register ready to accept new data |

| IARXRDY                |      | D1      |      | R1 (status) valid data available in receiver A holding register       |

| CLCK IN/OUT            |      | D1      | _    | R3 (command) _ input/output control for 62.5 kHz pin                  |

| DLEN A/DLIM A          |      | D0      | -    | R3 (command) – 3-line/2-line control for IBUS A receiver.             |

| Associated pins:       |      |         |      |                                                                       |

| DATA A                 | _    | input   |      | receiver A data input                                                 |

| DLIM A/DLEN A          |      | input   |      | receiver A data clock or bus enable signal                            |

| DATA B                 |      | 1/0     | -    | receiver B data input/transmitter B data output                       |

| DLIM B                 |      | 1/0     |      | receiver B data clock input/transmitter B data clock output           |

| DLEN B                 |      | 1/0     |      | receiver B bus enable input/transmitter B bus enable output           |

| IBCLCK                 |      | 1/0     | -    | 62.5 kHz clock input/output                                           |

#### Operation

All three IBUS circuits (receiver A, receiver B, and transmitter B) are capable of handling variable length codes from 1 to 12 bits. (In fact 15 bits can be transmitted 12 being data the rest being trailing zero's, and 15 bits may be received but only the last 12 being retained). Each of the three circuits have two 8-bit registers which are accessed by two successive read or write operations to the same address. There is a pointer for each pair of registers which selects the first or second byte. The pointers act in a bistable fashion with each access and are reset to point to the first byte with power on, D5 set in R3, or by reading either of the status registers R0 and R1. The two bytes of data in each holding register contain 12 bits of message, and 4-bits which specify the word length of message. For the transmitter the word length is used to generate the correct number of data clocks, for the receivers it may be used to identify the source of the message, or to establish that the message was a valid length.

The contents of each receiver register pair is organised as:

| 1st byte                                | D7              | D6     | D5         | D4          | D3           | D   | 2  | D1     | D     | 0     |

|-----------------------------------------|-----------------|--------|------------|-------------|--------------|-----|----|--------|-------|-------|

| RXA – R10A <sup>–</sup><br>RXB – R11A _ | L – 4           | L — 5  | L-6        | L – 7       | L – 8        | L – | 9  | L – 10 | D L - | - 11  |

| 2nd byte                                | D7              |        | D6         | D5          | D            | 4   | D3 | D2     | D1    | DO    |

| RXA – R10B<br>RXB – R11B                | Word ler<br>MSB | ~ IVVC | ord length | Word length | Word I<br>LS |     | L  | L – 1  | L – 2 | L – 3 |

Where L, L - 1 etc. means last data bit received, last minus one etc.

364

Fig. 13 IBUS block diagram

| 1st byte   | D7                 | D6 | D5 | D4          | D3                 | D2 | D  | I  | D <b>0</b> |    |

|------------|--------------------|----|----|-------------|--------------------|----|----|----|------------|----|

| TXB - R11A | 8                  | 7  | 6  | 5           | 4                  | 3  | 2  |    | 1          |    |

| 2nd byte   | D7                 | D  | 6  | D5          |                    | D4 | D3 | D2 | D1         | D0 |

| TXB - R11B | Word length<br>MSB |    |    | Word length | Word length<br>LSB |    | 12 | 11 | 10         | 9  |

Where 1, 2, etc. means first data bit transmitted, second data bit transmitted, etc.

IARXRDY or IBRXRDY (D1 in status registers R1 and R0) are set when a message has been received by RXA or RXB respectively. These flags also inhibit the receive holding registers from being overwritten by subsequent messages until the holding registers have been read. Reading a holding register pair will reset the relevant IARXRDY or IBRXRDY flags.

Transmitter B is initiated by writing two bytes to the transmit holding register (R11). This sets IBTXRDY to '0'. The DLIM line is sampled to detect the line busy state, and when the line is free a time out starts. If further DLIM's are detected before the end of the time out period the time out is reset and the sequence will begin again. When the time out has been completed the contents of the holding register are transferred to the output shift register and word length counter. The data and correct number of data clocks are then transmitted, at the completion of which IBTXRDY is returned to a '1'. New data should not be written to the transmit holding register (R11) while IBTXRDY = '0'. If the line is busy when a transmission is requested, the transmission will not start until  $300 - 330 \, \mu$ s after the line becomes free (last DLIM). Receiver B is inhibited from receiving data transmitted by transmitter B.

Receiver A may operated either as a two line receiver with DATA and DLIM, or as a three line DATA, DLEN and CLK receiver. DLIM A/DLEN A use the same pin, the function of which is selected by the DLEN A/DLIM A command D0, register R3 (command).

The 62.5 kHz clock (pin IBCLCK) may be used either as an input for receiver A (as described above), or to synchronise transmitter B outputs, or as an output synchronous with transmitter B. The function is selected by CLCK IN/OUT command D1 in R3

#### Fig. 14 IBUS waveforms

#### PORT A

Associated register: R6 – bits 0 to 4 – read/write Associated pins: PA0 to PA4

#### Operation

This is a 5-bit general purpose input/output port. The outputs are latched and are open drain up to nominal 12 V.

The latches may be accessed by the microprocessor via BUS D0 to D7 by a read or write sequence to register R6. If any pin of the port is used as an input then its output latch must first be written with a '1'. This allows the external circuit to control the pin. The state of the pins may be read by the microprocessor by reading R6. If the supply to the open drain outputs is turned on before the V<sub>DD</sub> supply to the IC, then the PORT must first be cleared by writing 1's to the output latch before operation.

PORT A might typically be used in viewdata mode as an interface to a non-volatile memory in which telephone and password numbers may be stored.

#### PORT B

Associated register: R7 — bits 0 to 3 — read/write Associated pins: PB0 to PB3

#### Operation

This is a 4-bit general purpose input/output port. It behaves in exactly the same way as PORT A except that access is by addressing R7, and that outputs PB1 to PB3 are open drain to nominal 5 V. PB0 is open drain to nominal 12 V, and might typically be used in combined teletext/viewdata applications to control the Picture On function.

# APPENDIX Register map

| -            | D7           | D6           | D5             | D4            | D3            | D2            | D1                 | D0                   |                        |

|--------------|--------------|--------------|----------------|---------------|---------------|---------------|--------------------|----------------------|------------------------|

| RO           | LTXRDY<br>R  | LRXRDY<br>R  | LDCD<br>R      | LFERR<br>R    | LPERR<br>R    | LIDCD         | IBRXRDY<br>R       | IBTXRDY<br>R         | STATUS<br>REGISTER 0   |

| R1           | TTXRDY<br>R  | TRXRDY<br>R  | TDCD<br>R      | TFERR<br>R    | TPERR<br>R    |               | IARXRDY<br>R       |                      | STATUS<br>REGISTER 1   |

| R2           | LPO/E<br>R/W | LPEN<br>R/W  | 75/1200<br>R/W |               | TPO/E<br>R/W  | TPEN<br>R/W   |                    |                      | MODE<br>REGISTER       |

| R3           | LRXEN<br>R/W | LTXEN<br>R/W | RESET<br>R/W   | LDBEN<br>R/W  | TRXEN<br>R/W  | TTXEN<br>R/W  | CLCK IN/OUT<br>R/W | DLEN A/DLIM A<br>R/W | COMMAND                |

| R4           | PARITY       | B7           | B6             | B5            | B4            | B3            | B2                 | B1                   | LINE RECEIVE           |

| R            | B8 (R)       | R            | R              | R             | R             | R             | R                  | R                    | REGISTER               |

| R4           | PARITY<br>OR | B7           | B6             | B5            | B4            | 83            | B2                 | B1                   | LINE TRANSM<br>HOLDING |

| <u>w    </u> | B8 (W)       | W            | W              | • W           | W             | W             | w                  | W                    | REGISTER               |

| R5           | PARITY<br>OR | B7           | B6             | 85            | B4            | B3            | B2                 | B1 <sup>1</sup>      | TAPE RECEIV<br>HOLDING |

| ≞∖⊥          | B8 (R)       | R            | R              | R             | R             | R             | R                  | R                    | REGISTER               |

| R5           | PARITY<br>OR | B7           | B6             | 85            | В4            | B3            | B2                 | B1                   | TAPE TRANSM<br>HOLDING |

| w            | B8 (W)       | W            | W              | W             | W             | w             | w                  | w                    | REGISTER               |

| R6           |              |              |                | PA4<br>R/W    | PA3<br>R/W    | PA2<br>R/W    | PA1<br>R/W         | PA0<br>R/W           | PORT A                 |

| R7           |              |              |                |               | PB3<br>R/W    | PB2<br>R/W    | PB1<br>R/W         | PBO<br>R/W           | PORT B                 |

| R8           | UK/EUR       | 60s TIMER    | DIAL GO        | 1.5s TIMER    | DI 3          | DI 2          | DI 1               | DIO                  | DIAL CONTRO            |

|              | R/W          | R/W          | R/W            | R/W           | w             | W             | W .                | w                    | REGISTER               |

| R10 A        | 88<br>R      | B7<br>R      | B6<br>R        | B5<br>R       | B4<br>R       | B3<br>R       | B2<br>R            | B1<br>R              | IBUS A                 |

| R10 B        | WL3<br>R     | WL2<br>R     | -<br>WL1<br>B  | -<br>WL0<br>B | -<br>B12<br>R | -<br>B11<br>B | _<br>B10<br>R      | <br>B9<br>R          | REGISTERS              |

SAA5070

#### DEVELOPMENT DATA

#### APPENDIX

Register map (continued)

|       | D7              | D6         | D5         | D4              | D3             | D2              | D1              | D0             |           |

|-------|-----------------|------------|------------|-----------------|----------------|-----------------|-----------------|----------------|-----------|

| R11 A | B8<br>R/W       | B7<br>R/W  | B6<br>R/W  | B5<br>R/W       | B4<br>R/W      | B3<br>R/W       | B2<br>R/W       | B1<br>R/W      | IBUS B    |

| R11B  | −<br>WL3<br>R/W | WL2<br>R/W | WL1<br>R/W | -<br>WLO<br>R/W | <br>B12<br>R/W | –<br>B11<br>R/W | –<br>B10<br>R/W | _<br>B9<br>R/W | REGISTERS |

## NOTE R9 is unused.

For details of bit movement in R10 and R11 see discussion of IBUS operation. A mnemonic list for use with this register map and Fig.1b is given on the next page.

## MNEMONIC LIST

| ALE           | address latch enable from microprocessor                                        |

|---------------|---------------------------------------------------------------------------------|

| CLCK IN/OUT   | input/output control for 62.5 kHz clock pin                                     |

| CPNTR         | pointer signal for two byte registers                                           |

| DLEN A/DLIM A | three line/two line control for IBUS A receiver                                 |

| DON           | dial off normal relay control for dialling                                      |

| IMP           | impulsing relay control for dialling                                            |

| IARXRDY       | IBUS A receiver ready – data available                                          |

| IBRXRDY       | IBUS B receiver ready – data available                                          |

| IBTXRDY       | IBUS B transmitter ready - previous transmission complete                       |

| LDBEN         | line demodulator output buffer enable                                           |

| LDCD          | line data carrier detected                                                      |

| LFERR         | line receiver framing error - received stop bit not HIGH                        |

| LIDCD         | line instantaneous data carrier detect                                          |

| LPEN          | line parity enable command                                                      |

| LPERR         | line receiver parity error flag                                                 |

| LPO/E         | line parity odd/even command                                                    |

| LRXEN         | line receiver enable                                                            |

| LRXRDY        | line receiver ready – data available                                            |

| LTXEN         | line transmitter and modulator enable                                           |

| LTXRDY        | line transmitter ready — transmit holding register empty                        |

| SRn           | select register 'n'                                                             |

| TDCD          | tape data carrier detected                                                      |

| TFERR         | tape receiver framing error - received stop bit not HIGH                        |

| TPEN          | tape parity enable command                                                      |

| TPERR         | tape receiver parity error flag                                                 |

| TPO/E         | tape parity odd/even command                                                    |

| TRXEN         | tape receiver enable                                                            |

| TRXRDY        | tape receiver ready — data available                                            |

| TTXEN         | tape transmitter enable                                                         |

| TTXRDY        | tape transmitter ready — transmit holding register empty                        |

| UK/EUR        | impulsing ratio control for UK and European standards                           |

| 75/1200       | baud rate selection command for line modulator and line transmit shift register |