## 54LS/74LS670

## **DESCRIPTION**

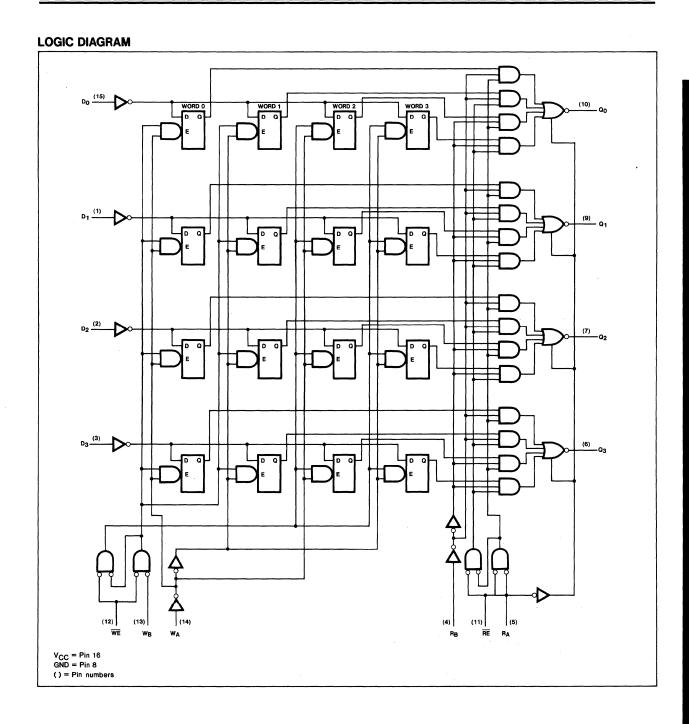

The "670" is a 4-by-4 Register File with 3-State outputs organized as 4-words of 4bits. Simultaneous read and write operation is allowed by separate read and write inputs, both address and enable. An almost unlimited number of devices can be stacked to increase the word capacity by tying the 3state outputs together. Any number of these devices can be operated in parallel to generate an n-bit word.

## **FEATURES**

- Simultaneous and independent **Read and Write operations**

- · Expandable to almost any word size and bit length

- 3-State outputs

- See "170" for open collector version

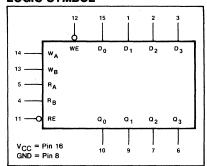

## **LOGIC SYMBOL**

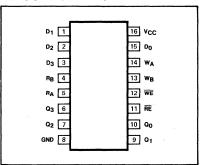

## **PIN CONFIGURATION**

## ORDERING CODE (See Section 9 for further Package and Ordering Information)

|             | · · · · · · · · · · · · · · · · · · ·                                     |                                                                          |

|-------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------|

| PACKAGES    | COMMERCIAL RANGES<br>V <sub>CC</sub> =5V±5%; T <sub>A</sub> =0°C to +70°C | MILITARY RANGES V <sub>CC</sub> =5V±10%; T <sub>A</sub> =-55°C to +125°C |

| Plastic DIP | N74LS670N                                                                 |                                                                          |

| Ceramic DIP | N74LS670F                                                                 | S54LS670F                                                                |

| Flatpak     |                                                                           | S54LS670W                                                                |

## INPUT AND OUTPUT LOADING AND FAN-OUT TABLE (a)

| PINS                            | DESCRIPTION                     |                                              | 54/74 | 545/745 | 54LS/74LS           |

|---------------------------------|---------------------------------|----------------------------------------------|-------|---------|---------------------|

| D <sub>0</sub> -D <sub>3</sub>  | Data inputs                     | I <sub>IH</sub> (μΑ)<br>I <sub>IL</sub> (mA) |       |         | 20<br>-0.4          |

| w <sub>A</sub> , w <sub>B</sub> | Write address inputs            | l <sub>IH</sub> (μΑ)<br>l <sub>IL</sub> (mA) |       |         | 20<br>-0.4          |

| WE                              | Write Enable (active LOW) input | I <sub>IH</sub> (μΑ)<br>I <sub>IL</sub> (mA) |       |         | 40<br>-0.8          |

| R <sub>A</sub> , R <sub>B</sub> | Read address inputs             | I <sub>IH</sub> (μΑ)<br>I <sub>IL</sub> (mA) |       |         | 20<br>-0.4          |

| RE                              | Read Enable (active LOW) input  | l <sub>IH</sub> (μΑ)<br>l <sub>IL</sub> (mA) |       |         | 40<br>-0.8          |

| Q <sub>0</sub> -Q <sub>3</sub>  | Outputs                         | I <sub>OH</sub> (mA)                         |       |         | -1/-2.6(a<br>4/8(a) |

## DC CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE (d)

| PARAMETER |                     | TEST CONDITIONS       |                         | 54/74 |     | 54S/74S 54LS/74 |     | 74LS   |     |      |

|-----------|---------------------|-----------------------|-------------------------|-------|-----|-----------------|-----|--------|-----|------|

|           |                     |                       |                         | Min   | Max | Min             | Max | Min    | Max | UNIT |

|           |                     | Voc = Min             | IOH =-1.0mA             |       |     |                 |     | 2.4    |     | V    |

| VOH       | Output HIGH voltage |                       | I <sub>OH</sub> =-2.6mA |       |     |                 |     | 2.4(e) |     | ٧    |

| Icc       | Supply current      | V <sub>CC</sub> = Max |                         |       |     |                 |     |        | 50  | mA   |

## NOTES

- a. The slashed numbers indicate different parametric values for Military/Commercial e. This parameter for Commercial range only. temperature ranges respectively.

- d. For family dc characteristics, see inside front cover for 54/74 and 54H/74H, and see inside back cover for 54S/74S and 54LS/74LS specifications.

## **FUNCTIONAL DESCRIPTION**

The "670" is a 16-bit 3-State Register File organized as 4-words of 4-bits each. Separate read and write address and enable inputs are available permitting simultaneous writing into one word location and reading from another location. The 4-bit word to be stored is presented to four data inputs. The Write Address inputs (WA & WB) determine the location of the stored word. When the Write Enable (WE) input is LOW, the data is entered into the addressed location. The addressed location remains transparent to the data while the WE is LOW. Data supplied at the inputs will be read out in true (non-inverting) form from the 3-state outputs. Data and Write Address inputs are inhibited when WE is HIGH.

Direct acquisition of data stored in any of the four registers is made possible by individual Read Address inputs (RA & RB). The addressed word appears at the four outputs when the Read Enable (RE) is LOW. Data outputs are in the high impedance "off" state when the Read Enable input is HIGH. This permits outputs to be tied together to increase the word capacity to very large numbers.

Up to 128 devices can be stacked to increase the word size to 512 locations by tying the 3-state outputs together. Since the limiting factor for expansion is the output HIGH current, further stacking is possible by tying pull up resistors to the outputs to increase the IOH current available. Design of the Read Enable signals for the stacked devices must ensure that there is no overlap in the LOW levels which would cause more than one output to be active at the same time. Parallel expansion to generate n-bit words is accomplished by driving the enable and address inputs of each device in parallel.

## WRITE MODE SELECT TABLE

| OPERATING  | INP | UTS | INTERNAL   |

|------------|-----|-----|------------|

| MODE       | WE  | Dn  | LATCHES(b) |

| Write Data | L   | · L | L .        |

|            | L   | l H | Н          |

| Data       |     |     |            |

| Latched    | н   | X   | no change  |

b. The Write Address (W<sub>A</sub> & W<sub>B</sub>) to the "internal latches" must be stable while WE is LOW for conventional oper-

## **READ MODE SELECT TABLE**

|                   |    | INPUTS                             | OUTPUTS |

|-------------------|----|------------------------------------|---------|

| OPERATING<br>MODE | RE | INTERNAL<br>LATCHES <sup>(c)</sup> | Qn      |

| Read              | L  | L                                  | , L     |

|                   | L  | Н                                  | Н       |

| Disabled          | Ξ  | х                                  | (Z)     |

### NOTE

- c. The Read Address (RA & RB) changes to select the "internal latches" are not constrained by WE or RE operation.

- H = HiGH voltage level L = LOW voltage level

- (Z) = High impedance "off" state

## AC CHARACTERISTICS: TA=25°C (See Section 4 for Test Circuits and Conditions)

| PARAMETER    |                                             |                                | 54/74 |     | 548/748 |     | 54LS/74LS  C <sub>L</sub> = 15pF  R <sub>L</sub> = 2kΩ |          | UNIT     |

|--------------|---------------------------------------------|--------------------------------|-------|-----|---------|-----|--------------------------------------------------------|----------|----------|

|              |                                             | TEST CONDITIONS                |       |     |         |     |                                                        |          |          |

|              |                                             |                                | Min   | Max | Min     | Max | Min                                                    | Max      |          |

| tPLH<br>tPHL | Propagation delay<br>Read Address to output | Figure 2                       |       |     |         |     |                                                        | 40<br>45 | ns<br>ns |

| tPLH<br>tPHL | Propagation delay<br>Write Enable to output | Figure 1                       |       |     |         |     | 4                                                      | 45<br>50 | ns<br>ns |

| tPLH<br>tPHL | Propagation delay<br>Data to output         | Figure 1                       |       |     |         |     |                                                        | 45<br>40 | ns<br>ns |

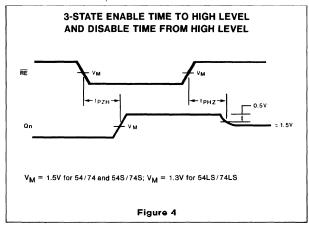

| tpzH         | Read enable time to HIGH level              | Figure 4                       |       |     |         |     |                                                        | 35       | ns       |

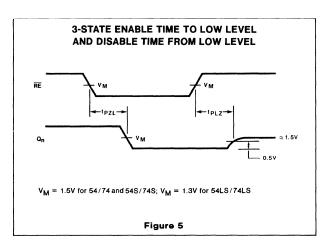

| tPZL         | Read enable time to LOW level               | Figure 5                       |       |     |         |     |                                                        | 40       | ns       |

| tPHZ         | Disable time from HIGH level                | Figure 4, C <sub>L</sub> = 5pF |       |     |         |     |                                                        | 50       | ns       |

| tPLZ         | Disable time from LOW level                 | Figure 5, C <sub>L</sub> = 5pF |       |     |         |     |                                                        | 35       | ns       |

## AC SETUP REQUIREMENTS: T<sub>A</sub> = 25°C (See Section 4 for Test Circuits and Conditions)

|    |                                              |                 | 54/74 |     | 545/745 |     | 54LS/74LS |     |      |

|----|----------------------------------------------|-----------------|-------|-----|---------|-----|-----------|-----|------|

|    | PARAMETER                                    | TEST CONDITIONS | Min   | Max | Min     | Max | Min       | Max | UNIT |

| tw | Write Enable pulse width                     | Figure 3        |       |     |         |     | 25        |     | ns   |

| ts | Setup time Data to positive going WE         | Figure 3        |       |     |         |     | 10        |     | ns   |

| th | Hold time Data to positive going WE          | Figure 3        |       |     |         |     | 15        |     | ns   |

| ts | Setup time Read Address to negative going WE | Figure 3        |       |     |         |     | 15        |     | ns   |

| th | Hold time Read Adress to positive going WE   | Figure 3        |       |     |         |     | 5.0       |     | ns   |

## **AC WAVEFORMS**

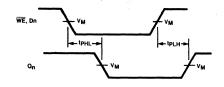

# PROPAGATION DELAY, WRITE ENABLE AND DATA TO OUTPUTS

$V_{M} = 1.5V$  for 54/74 and 54S/74S;  $V_{M} = 1.3V$  for 54LS/74LS

Figure 1

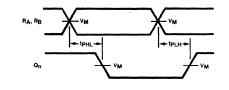

# PROPAGATION DELAY READ ADDRESS TO OUTPUTS

$V_{M} = 1.5V$  for 54/74 and 54S/74S;  $V_{M} = 1.3V$  for 54LS/74LS

Figure 2

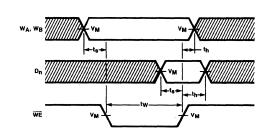

# SETUP AND HOLD TIMES WRITE ADDRESS AND DATA TO WRITE ENABLE

$V_{M} = 1.5V$  for 54/74 and 54S/74S;  $V_{M} = 1.3V$  for 54LS/74LS

The shaded areas indicate when the input is permitted to change for predictable output performance.

Figure 3

## AC WAVEFORMS (Cont'd